# Precision Remote Diode Temperature Sensor with SMBus Interface and TruTherm<sup>™</sup> Technology

Check for Samples: LM95235, LM95235-Q1

# **FEATURES**

- **Remote and Local Temperature Channels**

- **TruTherm BJT Beta Compensation Technology**

- LM95235Q is AEC-Q100 Grade 3 Compliant and is Manufactured on an Automotive Grade Flow

- Diode Model Selection Bit MMBT3904 or 65/90-nm Processor Diodes

- Two Formats: -128°C to 127.875°C and 0°C to 255.875°C

- **Digital Filter for Remote Channel**

- **Programmable TCRIT and OS Thresholds**

- **Programmable Shared Hysteresis Register**

- **Diode Fault Detection**

- Mask, Offset, and Status Registers

- SMBus 2.0 Compatible Interface, Supports TIMEOUT

- **Programmable Conversion Rate for Best** Power Consumption

- **Three-Level Address Pin**

- Standby Mode One-Shot Conversion Control

- Pin-for-Pin Compatible With the LM86 and • LM89

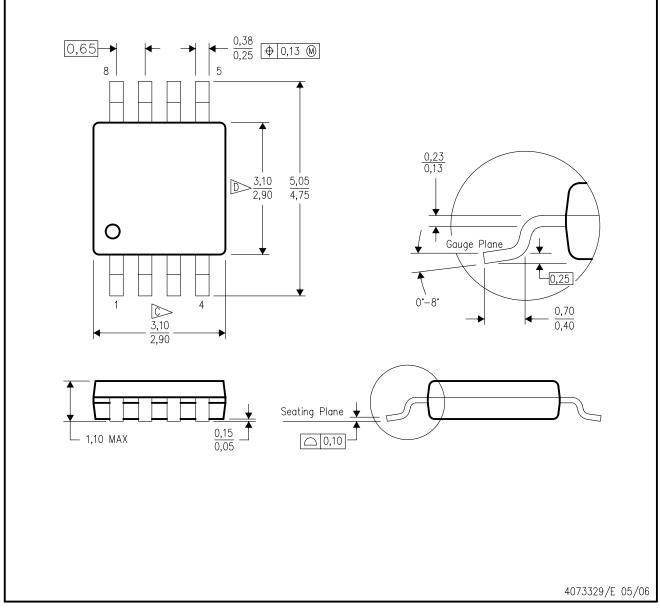

- 8-Pin VSSOP Package

# APPLICATIONS

- **Processor/Computer System Thermal** ٠ Management (For Example, Laptops, Desktops, Workstations, Servers)

- **Electronic Test Equipment and Office** Electronics

# **KEY SPECIFICATIONS**

- Supply Voltage 3.0 to 3.6 V •

- Supply Current, Conv. Rate = 1 Hz 350 µA (typ) •

- **Remote Diode Temperature Accuracy**

- $T_A = 25^{\circ}C$  to  $85^{\circ}C$ ;  $T_D = 60^{\circ}C$  to  $100^{\circ}C$ ,  $\pm 0.75$ °C (max)

- $T_A = 25^{\circ}C$  to 90°C;  $T_D = 40^{\circ}C$  to 125°C, ±1.5 °C (max)

- Local Temperature Accuracy

- $T_A = 25^{\circ}C$  to 100°C, ±2.0 °C (max)

- Conversion Rate, Both Channels 16 to 0.4 Hz

# DESCRIPTION

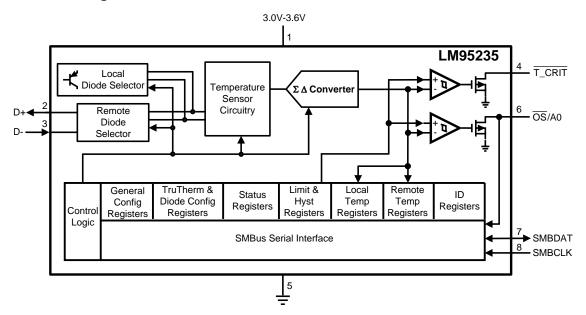

The LM95235 is an 11-bit digital temperature sensor with a 2-wire System Management Bus (SMBus) interface and TruTherm technology that can monitor the temperature of a remote diode as well as its own temperature. The LM95235 can be used to very accurately monitor the temperature of external microprocessors, graphics devices such as processors, or a diode-connected MMBT3904 transistor. For automotive applications the LM95235Q is available that is AEC-Q100 Grade3 compliant and is manufactured on an Automotive Grade Flow. TruTherm BJT (transistor) beta compensation technology allows the LM95235 to precisely monitor thermal diodes found in 90 nm and smaller geometry processes. LM95235 reports temperature in two different formats for +127.875°C/-128°C range and 0°C/255°C range. The LM95235 T\_CRIT and OS outputs are asserted when either unmasked channel exceeds its programmed limit and can be used to shutdown the system, to turn on the system fans, or as a microcontroller interrupt function. The current status of the  $\overline{T_CRIT}$  and  $\overline{OS}$  pins can be read back from the status registers via the SMBus interface. All limits have a shared programmable hysteresis register.

The remote temperature channel of the LM95235 has a programmable digital filter. The LM95235 contains a diode model selection bit to select between a typical Intel® processor on a 65 nm or 90 nm process or MMBT3904, as well as an offset register for maximum flexibility and best accuracy.

Δ**Α**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

# LM95235 LM95235-Q1

SNIS142F-APRIL 2006-REVISED MARCH 2013

# **DESCRIPTION (CONTINUED)**

The LM95235 has a three-level address pin to connect up to 3 devices to the same SMBus master, that is shared with the OS output. The LM95235 has a programmable conversion rate register and a standby mode to save power. One conversion can be triggered in standby mode by writing to the one-shot register.

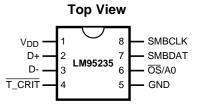

# **Connection Diagram**

Figure 1. VSSOP-8 Package See package number DGK0008A

# Simplified Block Diagram

### **Table 1. Pin Descriptions**

| Pin<br>Number | Name              | Туре                                                       | Description                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|---------------|-------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

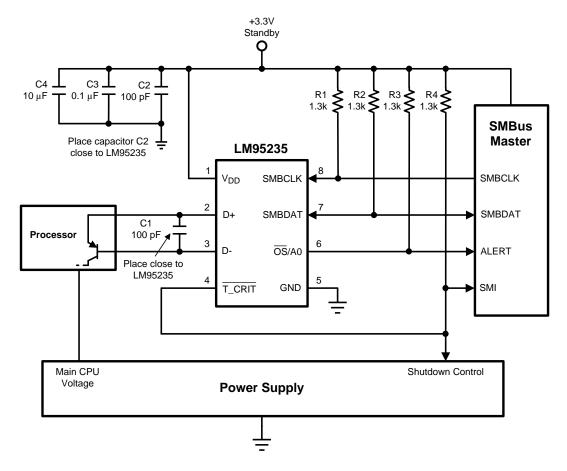

| 1             | V <sub>DD</sub>   | Power                                                      | Device power supply. Requires bypass capacitor of 10 $\mu F$ in parallel with 0.1 $\mu F$ and 100 pF. Place 100 pF closest to device pin.                                                                                                                                                                                                                  |  |  |  |

| 2             | D+                | Analog Input/Output                                        | Analog Input/Output Positive input from the thermal diode.                                                                                                                                                                                                                                                                                                 |  |  |  |

| 3             | D-                | Analog Input/Output Negative input from the thermal diode. |                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 4             | T_CRIT            | Digital Output                                             | Critical temperature output. Open-drain output requires pull-up resistor. Active low.                                                                                                                                                                                                                                                                      |  |  |  |

| 5             | GND               | Ground                                                     | Device ground.                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 6             | <del>OS</del> /A0 | Digital Input/Output                                       | Over-temperature shutdown comparator output or SMBus slave address input. Defaults as an SMBus slave address input that selects one of three addresses. Can be tied to $V_{DD}$ , GND, or to the middle of a resistor divider connected between $V_{DD}$ and GND. When programmed as an $\overline{OS}$ comparator output it is active low and open drain. |  |  |  |

| 7             | SMBDAT            | Digital Input/Output                                       | SMBus interface data pin. Open-drain output requires pull-up resistor.                                                                                                                                                                                                                                                                                     |  |  |  |

| 8             | SMBCLK            | Digital Input                                              | SMBus interface clock pin.                                                                                                                                                                                                                                                                                                                                 |  |  |  |

# **Typical Application**

# LM95235 LM95235-Q1

SNIS142F-APRIL 2006-REVISED MARCH 2013

www.ti.com

RUMENTS

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# Absolute Maximum Ratings<sup>(1)</sup>

|                      | -0.3V to 6.0V           |

|----------------------|-------------------------|

|                      | -0.5V to 6.0V           |

|                      | (V <sub>DD</sub> +0.3V) |

|                      | ±1 mA                   |

|                      | ±5 mA                   |

|                      | 10 mA                   |

|                      | 30 mA                   |

| Human Body Model     | 2500V                   |

| Machine Model        | 250V                    |

| Charged Device Model | 1000V                   |

|                      | +125°C                  |

|                      | -65°C to +150°C         |

|                      | Machine Model           |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is guaranteed to be functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions. Operation of the device beyond the maximum Operating Ratings is not recommended.

- (2) When the input voltage (V<sub>1</sub>) at any pin exceeds the power supplies (V<sub>1</sub> < GND or V<sub>1</sub> > V<sub>DD</sub>), the current at that pin should be limited to 5 mA. Parasitic components and or ESD protection circuitry are shown in the figures in Table 2 for the LM95235's pins. Care should be taken not to forward bias the parasitic diodes on pins 2 and 3. Doing so by more than 50 mV may corrupt the temperature measurements. SNP refers to Snap-back device.

- (3) Human body model (HBM) is a charged 100 pF capacitor discharged into a 1.5 kΩ resistor. Machine model (MM), is a charged 200 pF capacitor discharged directly into each pin. Charged Device Model (CDM) simulates a pin slowly acquiring charge (such as from a device sliding down the feeder in an automated assembler) then rapidly being discharged.

- (4) Thermal resistance junction-to-ambient when attached to a printed circuit board with 1 oz. foil and no airflow is: θ<sub>JA</sub> for VSSOP-8 package = 210°C/W

| Pin No. | Label           | Circuit | Pin ESD Protection | n Structure Circuits                  |

|---------|-----------------|---------|--------------------|---------------------------------------|

| 1       | V <sub>DD</sub> | А       |                    |                                       |

| 2       | D+              | А       | V+                 |                                       |

| 3       | D-              | А       |                    |                                       |

| 4       | T_CRIT          | В       |                    |                                       |

| 5       | GND             | А       |                    | i i i i i i i i i i i i i i i i i i i |

| 6       | OS/A0           | В       |                    |                                       |

| 7       | SMBDAT          | В       | GND Circuit A      | Circuit B                             |

| 8       | SMBCLK          | В       |                    |                                       |

### **Table 2. ESD Protection**

# **Operating Ratings** <sup>(1)</sup>

| Operating Temperature Range                                                                                                        | -40°C to +125°C |                                       |  |

|------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------------|--|

|                                                                                                                                    | LM95235CIMM     | $0^{\circ}C \le T_A \le +90^{\circ}C$ |  |

| Electrical Characteristics Temperature Range, $T_{MIN} \le T_A \le T_{MAX}$                                                        | LM95235DIMM     | -40°C ≤ T <sub>A</sub> ≤ +90°C        |  |

|                                                                                                                                    | LM95235EIMM     | -40°C ≤ T <sub>A</sub> ≤ +90°C        |  |

|                                                                                                                                    | LM95235QEIMM    | -40°C ≤ T <sub>A</sub> ≤ +85°C        |  |

| Supply Voltage (V <sub>DD</sub> )                                                                                                  | +3.0V to +3.6V  |                                       |  |

| Soldering process must comply with Reflow Temperature Profile specifications. Refer to http://www.ti.com/packaging. <sup>(2)</sup> |                 |                                       |  |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is guaranteed to be functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions. Operation of the device beyond the maximum Operating Ratings is not recommended.

(2) Reflow temperature profiles are different for packages containing lead (Pb) than for those that do not.

Copyright © 2006–2013, Texas Instruments Incorporated

#### **Temperature-to-Digital Converter Characteristics**

Unless otherwise noted, these specifications apply for  $V_{DD} = +3.0$  Vdc to 3.6 Vdc. **Boldface limits apply for T\_A = T\_J = T\_{MIN} \le T\_A \le T\_{MAX};** all other limits  $T_A = T_J = +25^{\circ}$ C, unless otherwise noted.  $T_J$  is the junction temperature of the LM95235.  $T_A$  is the ambient temperature of the LM95235.  $T_D$  is the junction temperature of the remote thermal diode.

| Parameter                                                 | Test Co                                                                                          | nditions                            | Typical<br>(1) | LM95235<br>CIMM<br>Limits<br>(2) | LM95235<br>DIMM<br>Limits<br>(2) | LM95235<br>EIMM<br>LM95235<br>QEIMM<br>Limits<br>(2) | Unit     |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------|----------------|----------------------------------|----------------------------------|------------------------------------------------------|----------|

| Temperature Accuracy                                      | $T_A = 25^{\circ}C \text{ to } +100^{\circ}C$                                                    |                                     | ±1             | ±2                               | ±2                               | ±2                                                   | °C (max) |

| Using Local Diode <sup>(3)</sup>                          | $T_A = -40^{\circ}C$ to $+25^{\circ}C$                                                           |                                     |                |                                  | ±6.0                             | ±6.0                                                 | °C (max) |

| Temperature Accuracy<br>Using Remote Diode <sup>(4)</sup> | $T_A = +25^{\circ}C \text{ to } +85^{\circ}C;$<br>$T_D = +60^{\circ}C \text{ to } +100^{\circ}C$ | 65nm Intel Processor                | ±0.5           | ±0.75                            | ±0.75                            | ±0.75                                                | °C (max) |

|                                                           | $T_A = +25^{\circ}C \text{ to } T_{MAX};$<br>$T_D = +60^{\circ}C \text{ to } +100^{\circ}C$      | MMBT3904 or<br>65nm Intel Processor | ±0.5           | ±1.0                             | ±1.0                             | ±1.0                                                 | °C (max) |

|                                                           | $T_A = +25^{\circ}C \text{ to } T_{MAX};$<br>$T_D = +40^{\circ}C \text{ to } +120^{\circ}C$      | MMBT3904 or<br>65nm Intel Processor | ±0.75          | ±1.5                             | ±1.5                             | ±1.5                                                 | °C (max) |

|                                                           | $T_A = -40$ °C to +25°C;<br>$T_D = +25$ °C to +125°C                                             | MMBT3904 or<br>65nm Intel Processor |                |                                  | ±3.0                             |                                                      | °C (max) |

|                                                           | $T_A = -40$ °C to +25°C;<br>$T_D = +25$ °C to +125°C                                             | MMBT3904                            |                |                                  |                                  | ±3.0                                                 | °C (max) |

|                                                           | $T_A = -40$ °C to +25°C;<br>$T_D = -40$ °C to +25°C                                              | MMBT3904                            |                |                                  | ±5.0                             | ±5.0                                                 | °C (max) |

|                                                           | Digital Filter Off                                                                               |                                     | 11             |                                  |                                  |                                                      | Bits     |

| Remote Diode                                              |                                                                                                  |                                     | 0.125          |                                  |                                  |                                                      | °C       |

| Measurement Resolution                                    | Digital Filter On                                                                                |                                     | 13             |                                  |                                  |                                                      | Bits     |

|                                                           |                                                                                                  |                                     | 0.03125        |                                  |                                  |                                                      | °C       |

| Local Diode Measurement                                   |                                                                                                  |                                     | 11             |                                  |                                  |                                                      | Bits     |

| Resolution                                                |                                                                                                  | 0.125                               |                |                                  |                                  | °C                                                   |          |

| Conversion Time, Fastest                                  | Local and Remote Channels<br>Local or Remote Channels                                            |                                     | 63             | 72                               | 72                               | 72                                                   | ms (max) |

| Setting <sup>(5)</sup>                                    |                                                                                                  |                                     | 33             |                                  |                                  |                                                      | ms       |

| Quiescent Current                                         | SMBus Inactive, 1 Hz con                                                                         | version rate <sup>(6)</sup>         | 350            | 650                              | 650                              | 650                                                  | µA (max) |

| Quiescent Current                                         | Standby Mode                                                                                     |                                     | 300            |                                  |                                  |                                                      | μA       |

| D- Source Voltage                                         |                                                                                                  |                                     | 400            |                                  |                                  |                                                      | mV       |

| External Diode Current                                    | High-level                                                                                       |                                     | 172            | 225                              | 225                              | 225                                                  | µA (max) |

| Source                                                    | Low-level                                                                                        |                                     | 10.75          |                                  |                                  |                                                      | μA       |

| Diode Source Current Ratio                                |                                                                                                  |                                     | 16             |                                  |                                  |                                                      |          |

| Dower On Deast Voltage                                    |                                                                                                  |                                     |                | 2.8                              | 2.8                              | 2.8                                                  | V (max)  |

| Power-On Reset Voltage                                    |                                                                                                  |                                     |                | 1.6                              | 1.6                              | 1.6                                                  | V (min)  |

| T_CRIT Pin Temperature<br>Threshold                       | Default                                                                                          |                                     | +110           |                                  |                                  |                                                      | °C       |

| OS Pin Temperature<br>Threshold                           | Default                                                                                          |                                     | +85            |                                  |                                  |                                                      | °C       |

(1) Typical figures are at  $T_A = 25^{\circ}C$  and represent most likely parametric norms at the time of product characterization. The typical specifications are not guaranteed.

(2) Limits are guaranteed to TI's AOQL (Average Outgoing Quality Level).

(3) Local temperature accuracy does not include the effects of self-heating. The rise in temperature due to self-heating is the product of the internal power dissipation of the LM95235 and the thermal resistance. See <sup>(1)</sup> for the thermal resistance to be used in the self-heating calculation.

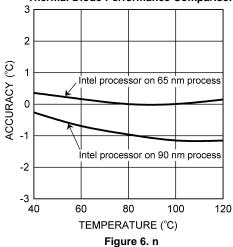

(4) The accuracy of the LM95235 is guaranteed when using a typical thermal diode of an Intel processor on a 65 nm process or an MMBT3904 diode-connected transistor, as selected in the Remote Diode Model Select register. See typical performance curve for performance with Intel processor on a 90nm process.

(5) This specification is provided only to indicate how often temperature data is updated. The LM95235 can be read at any time without regard to conversion state (and will yield last conversion result).

(6) Quiescent current will not increase substantially when the SMBus is active.

## **Logic Electrical Characteristics**

# **Digital DC Characteristics**

Unless otherwise noted, these specifications apply for  $V_{DD}$ = +3.0 Vdc to 3.6 Vdc. Boldface limits apply for  $T_A = T_J = T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = +25^{\circ}$ C, unless otherwise noted.

| Symbol                          | Parameter                                     | Test Conditions                                    | Typical <sup>(1)</sup> | Limits <sup>(2)</sup>  | Unit<br>(Limit)    |

|---------------------------------|-----------------------------------------------|----------------------------------------------------|------------------------|------------------------|--------------------|

| SMBDAT, SN                      | IBCLK INPUTS                                  |                                                    |                        |                        |                    |

| V <sub>IN(1)</sub>              | Logical "1" Input Voltage                     |                                                    |                        | 2.1                    | V (min)            |

| V <sub>IN(0)</sub>              | Logical "0" Input Voltage                     |                                                    |                        | 0.8                    | V (max)            |

| V <sub>IN(HYST)</sub>           | SMBDAT and SMBCLK Digital Input<br>Hysteresis |                                                    | 400                    |                        | mV                 |

| I <sub>IN(1)</sub>              | Logical "1" Input Current                     | $V_{IN} = V_{DD}$                                  | -0.005                 | -10                    | μA (max)           |

| I <sub>IN(0)</sub>              | Logical "0" Input Current                     | V <sub>IN</sub> = 0 V                              | 0.005                  | +10                    | μA (max)           |

| C <sub>IN</sub>                 | Input Capacitance                             |                                                    | 5                      |                        | pF                 |

| A0 DIGITAL I                    | NPUT                                          |                                                    |                        |                        |                    |

| V <sub>IH</sub>                 | Input High Voltage                            |                                                    |                        | 0.90 × V <sub>DD</sub> | V (min)            |

| V/                              |                                               |                                                    |                        | 0.57 × V <sub>DD</sub> | V (max)            |

| V <sub>IM</sub>                 | Input Middle Voltage                          |                                                    |                        | 0.43 × V <sub>DD</sub> | V (min)            |

| VIL                             | Input Low Voltage                             |                                                    |                        | 0.10 × V <sub>DD</sub> | V (max)            |

| I <sub>IN(1)</sub>              | Logical "1" Input Current                     | $V_{IN} = V_{DD}$                                  | -0.005                 | -10                    | μA (max)           |

| I <sub>IN(0)</sub>              | Logical "0" Input Current                     | V <sub>IN</sub> = 0 V                              | 0.005                  | +10                    | μA (max)           |

| C <sub>IN</sub>                 | Input Capacitance                             |                                                    | 5                      |                        | pF                 |

| SMBDAT, T_                      | CRIT, OS DIGITAL OUTPUTS                      |                                                    |                        |                        |                    |

| I <sub>OH</sub>                 | High Level Output Leakage Current             | $V_{OUT} = V_{DD}$                                 |                        | 10                     | μA (max)           |

| V <sub>OL(T_CRIT</sub> ,<br>OS) | T_CRIT, OS Low Level Output Voltage           | I <sub>OL</sub> = 6 mA                             |                        | 0.4                    | V (max)            |

| V <sub>OL(SMBDAT)</sub>         | SMBDAT Low Level Output Voltage               | $I_{OL} = 4 \text{ mA}$<br>$I_{OL} = 6 \text{ mA}$ |                        | 0.4<br>0.6             | V (max)<br>V (max) |

| C <sub>OUT</sub>                | Digital Output Capacitance                    |                                                    | 5                      |                        | pF                 |

Typical figures are at T<sub>A</sub> = 25°C and represent most likely parametric norms at the time of product characterization. The typical specifications are not guaranteed.

(2) Limits are guaranteed to TI's AOQL (Average Outgoing Quality Level).

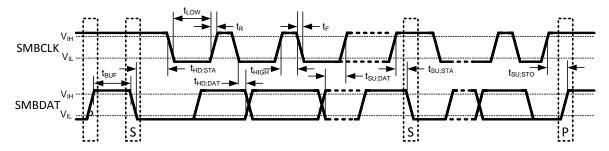

# **SMBus Digital Switching Characteristics**

Unless otherwise noted, these specifications apply for  $V_{DD}$ = +3.0 Vdc to +3.6 Vdc, C<sub>L</sub> (load capacitance) on output lines = 80 pF. **Boldface limits apply for T<sub>A</sub> = T<sub>J</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>**; all other limits T<sub>A</sub> = T<sub>J</sub> = +25°C, unless otherwise noted. The switching characteristics of the LM95235 fully meet or exceed the published specifications of the SMBus version 2.0. The following parameters are the timing relationships between SMBCLK and SMBDAT signals related to the LM95235. They

|                    | Parameter             | Test Conditions                         | Typical | Limits    | Unit                   |

|--------------------|-----------------------|-----------------------------------------|---------|-----------|------------------------|

|                    |                       |                                         | (1)     | (2)       | (Limit)                |

| f <sub>SMB</sub>   | SMBus Clock Frequency |                                         |         | 100<br>10 | kHz (max)<br>kHz (min) |

| t <sub>LOW</sub>   | SMBus Clock Low Time  | from $V_{IN(0)}$ max to $V_{IN(0)}$ max |         | 4.7<br>25 | µs (min)<br>ms (max)   |

| t <sub>HIGH</sub>  | SMBus Clock High Time | from $V_{IN(1)}$ min to $V_{IN(1)}$ min |         | 4.0       | µs (min)               |

| t <sub>R,SMB</sub> | SMBus Rise Time       | (3)                                     | 1       |           | µs (max)               |

| t <sub>F,SMB</sub> | SMBus Fall Time       | (4)                                     | 0.3     |           | µs (max)               |

(1) Typical figures are at  $T_A = 25^{\circ}C$  and represent most likely parametric norms at the time of product characterization. The typical specifications are not guaranteed.

(2) Limits are guaranteed to TI's AOQL (Average Outgoing Quality Level).

- (3) The output rise time is measured from (V<sub>IN(0)</sub>max 0.15V) to (V<sub>IN(1)</sub>min + 0.15V).

- (4) The output fall time is measured from  $(V_{IN(1)}min + 0.15V)$  to  $(V_{IN(0)}max 0.15V)$ .

- 6 Submit Documentation Feedback

### SMBus Digital Switching Characteristics (continued)

Unless otherwise noted, these specifications apply for  $V_{DD}$ = +3.0 Vdc to +3.6 Vdc,  $C_L$  (load capacitance) on output lines = 80 pF. **Boldface limits apply for T<sub>A</sub> = T<sub>J</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>;** all other limits T<sub>A</sub> = T<sub>J</sub> = +25°C, unless otherwise noted. The switching characteristics of the LM95235 fully meet or exceed the published specifications of the SMBus version 2.0. The

The switching characteristics of the LM95235 fully meet or exceed the published specifications of the SMBus version 2.0. The following parameters are the timing relationships between SMBCLK and SMBDAT signals related to the LM95235. They adhere to, but are not necessarily, the SMBus specifications.

|                      | Parameter                                                                                                 | Test Conditions                                                 | Typical | Limits      | Unit                 |

|----------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|---------|-------------|----------------------|

|                      |                                                                                                           |                                                                 | (1)     | (2)         | (Limit)              |

| t <sub>OF</sub>      | Output Fall Time                                                                                          | $C_L = 400 \text{ pF},$<br>$I_O = 3 \text{ mA},$ <sup>(4)</sup> |         | 250         | ns (max)             |

| t <sub>TIMEOUT</sub> | SMBDAT and SMBCLK Time Low for Reset of Serial Interface <sup>(5)</sup>                                   |                                                                 |         | 25<br>35    | ms (min)<br>ms (max) |

| t <sub>SU;DAT</sub>  | Data In Setup Time to SMBCLK High                                                                         |                                                                 |         | 250         | ns (min)             |

| t <sub>HD;DAT</sub>  | Data Out Stable after SMBCLK Low                                                                          |                                                                 |         | 300<br>1075 | ns (min)<br>ns (max) |

| t <sub>HD;STA</sub>  | Start Condition SMBDAT Low to<br>SMBCLK Low (Start condition hold<br>before the first clock falling edge) |                                                                 |         | 100         | ns (min)             |

| t <sub>SU;STO</sub>  | Stop Condition SMBCLK High to<br>SMBDAT Low (Stop Condition Setup)                                        |                                                                 |         | 100         | ns (min)             |

| t <sub>SU;STA</sub>  | SMBus Repeated Start-Condition Setup<br>Time, SMBCLK High to SMBDAT Low                                   |                                                                 |         | 0.6         | µs (min)             |

| t <sub>BUF</sub>     | SMBus Free Time Between Stop and Start Conditions                                                         |                                                                 |         | 1.3         | µs (min)             |

(5) Holding the SMBDAT and/or SMBCLK lines Low for a time interval greater than t<sub>TIMEOUT</sub> will reset the LM95235's SMBus state machine, therefore setting SMBDAT and SMBCLK pins to a high impedance state.

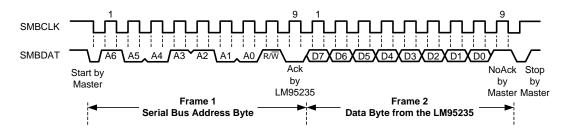

Figure 2. SMBus Communication

LM95235 LM95235-Q1 SNIS142F – APRIL 2006 – REVISED MARCH 2013

www.ti.com

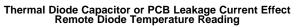

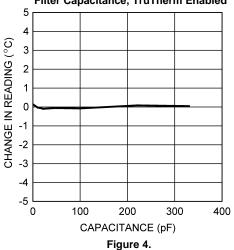

Remote Temperature Reading Sensitivity to Thermal Diode Filter Capacitance, TruTherm Enabled

Intel Processor on 65nm Process or 90nm Process Thermal Diode Performance Comparison

## FUNCTIONAL DESCRIPTION

The LM95235 is a temperature sensor that measures Local and Remote temperature zones. The LM95235 uses a  $\Delta V_{be}$  temperature sensing method. A differential voltage, representing temperature, is digitized using a Sigma-Delta analog to digital converter. TruTherm Technology allows the LM95235 to accurately sense the temperature of a thermal diode found on die fabricated using a sub-micron process. For more information on TruTherm Technology see Applications Hints . The LM95235 is compatible with the serial SMBus version 2.0 two-wire serial interface.

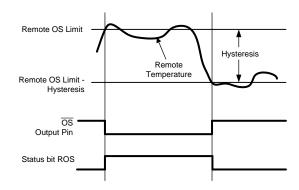

The LM95235 has  $\overline{OS}$  and  $\overline{TCRIT}$  open-drain digital outputs that indicate the state of the local and remote temperature readings when compared to user-programmable limits. If enabled, the local temperature is compared to the user-programmable Local Shared OS and TCRIT Limit Register (Default Value = 85°C). The comparison result can trigger the T\_CRIT pin and/or the  $\overline{OS}$  pin depending on the settings of the Local TCRIT Mask and OS Mask bits found in Configuration Register 1. The comparison result can also be read back from Status Register 1. If enabled, the remote temperature is compared to the user-programmable Remote TCRIT Limit Register (Default Value = 110°C), and the Remote OS Limit Register (Default Value = 85°C) values. The comparison result can trigger the T\_CRIT pin and/or the OS pin depending on the settings of Configuration Register 1. The following table describes the default temperature settings for each measured temperature that triggers T\_CRIT and/or OS pins:

| Output Pin | Remote,°C | Local,°C |

|------------|-----------|----------|

| T_CRIT     | 110       | 85       |

| OS         | 85        | 85       |

The following table describes the limit register mapping to the  $\overline{T_CRIT}$  and/or  $\overline{OS}$  pins:

| Output Pin | Remote             | Local                       |

|------------|--------------------|-----------------------------|

| T_CRIT     | Remote TCRIT Limit | Local Shared OS/TCRIT Limit |

| OS         | Remote OS Limit    | Local Shared OS/TCRIT Limit |

The  $\overline{T_CRIT}$  and  $\overline{OS}$  outputs are open-drain, active low.

The remote temperature readings support a programmable digital filter. Based on the settings in Configuration Register 2 a digital filter can be turned on to improve the noise performance of the remote temperature as well as to increase the resolution of the temperature reading. If the filter is enabled the filtered readings are used for TCRIT and <u>OS</u> comparisons. The LM95235 may be placed in low power consumption (Standby) mode by setting the STOP/RUN bit found in Configuration Register 1. In the Standby mode, the LM95235's SMBus interface remains active while all circuitry not required is turned off. In the Standby mode the host can trigger one round of conversions by writing to the One-Shot Register. The value written into this register is not kept. Local and Remote temperatures will be converted once and the T\_CRIT and OS pins will reflect the comparison results based on this set of conversions results.

All the temperature readings are in 16-bit left-justified word format. The 10-bit plus sign local temperature reading is contained in two 8-bit registers: Local Temp MSB and Local Temp LSB Registers. The remote temperature supports both a 13-bit unsigned and a 12-bit plus sign format. These readings are available in their corresponding registers as described in the LM95235 Register table. The lower 2-bits of the remote temperature reading will contain temperature information only if the digital filter is enabled. If the digital filter is disabled, these two bits will read back 0.

The signed and unsigned remote temperature readings are available simultaneously in separate registers, therefore allowing both negative temperatures and temperatures 128°C and above to be measured.

All Limit Registers support unsigned temperature format with 1°C LSb resolution. The Local Shared TCRIT and OS Limit Register is 7 bits for limits between 0°C and 127°C. The Remote Temperature TCRIT and OS Limit Registers are 8 bits each for limits between 0°C and 255°C.

# LM95235 LM95235-Q1

SNIS142F-APRIL 2006-REVISED MARCH 2013

# **CONVERSION SEQUENCE**

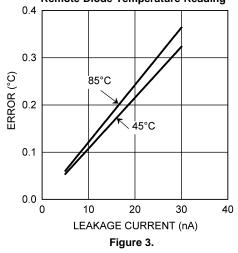

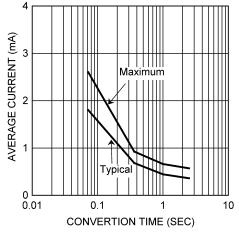

In the power-up default state the LM95235 takes a maximum of 1 second to convert the Local Temperature, Remote Temperature, and to update all of its registers. Only during the conversion process is the Busy bit (D7) in Status Register 1 (02h) high. These conversions are addressed in a round-robin sequence. The conversion rate may be modified by the Conversion Rate bits found in the Conversion Rate Register (R/W: 04h/0Ah). When the conversion rate is modified a delay is inserted between conversions, the actual maximum conversion time remains at 72 ms. Different conversion rates will cause the LM95235 to draw different amounts of supply current as shown in Figure 7.

Figure 7. Conversion Rate Effect on Power Supply Current

# **POWER-ON-DEFAULT STATES**

LM95235 always powers up to these known default states. The LM95235 remains in these states until after the first conversion.

- 1. Command Register set to 00h

- 2. Conversion Rate register defaults to 02h (1 second).

- 3. Local Temperature set to 0°C until the end of the first conversion

- 4. Remote Diode Temperature set to 0°C until the end of the first conversion

- 5. Remote OS limit default is 55h (85°C).

- 6. Local Shared and TCRIT limit default is 55h (85°C).

- 7. Remote TCRIT limit default is 6Eh (110°C).

- 8. Remote Offset High and Low bytes default to 00h.

- 9. Configuration Register 1 defaults to 00h. This sets the LM95235 as follows:

- (a) The STOP/RUN defaults to the active/converting mode.

- (b) The Local and Remote TCRIT and OS Masks are reset to 0.

- 10. Configuration Register 2 defaults to 1Fh. This sets the LM95235 as follows:

- (a) Remote Diode digital filter defaults on.

- (b) The Remote Diode mode defaults to a typical Intel processor on 65/90 nm process.

- (c) Diode Fault Mask bit for TCRIT defaults to 1.

- (d) Diode Fault Mask bit for OS defaults to 0.

- (e) Pin 6 Function defaults to Address Input function (A0).

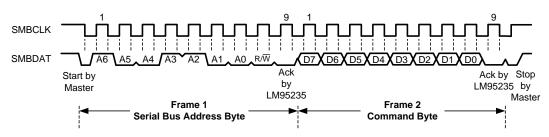

### SMBus INTERFACE

The LM95235 operates as a slave on the SMBus, so the SMBCLK line is an input and the SMBDAT line is bidirectional. The LM95235 never drives the SMBCLK line and it does not support clock stretching. According to SMBus specifications, the LM95235 has a 7-bit slave address. Three SMBus addresses can be selected by connecting pin 6 (A0) to either Low, Mid-Supply or High voltages. Table 3 shows the possible selections.

| Т | able | 3  | Address | Selection |

|---|------|----|---------|-----------|

|   | anic | э. | Audicaa | Jelection |

| State of the A0 Pin | SMBus Device Address |          |  |

|---------------------|----------------------|----------|--|

| State of the AU PIN | HEX                  | Binary   |  |

| Low                 | 18                   | 001 1000 |  |

| Mid-Supply          | 29                   | 010 1001 |  |

| High                | 4C                   | 100 1100 |  |

The  $\overline{OS}/A0$  pin, after power-up, defaults as an address select input pin (A0). After power-up, the  $\overline{OS}/A0$  pin can only be programmed as an OS output when it is in the "High" state. Therefore, 4Ch is the only valid slave address that can be used when the  $\overline{OS}/A0$  pin is programmed to function as an  $\overline{OS}$  output. When the  $\overline{OS}/A0$  pin is programmed to function as an  $\overline{OS}$  output. When the  $\overline{OS}/A0$  pin is programmed to function as an  $\overline{OS}$  output. When the  $\overline{OS}/A0$  pin is programmed to function as an  $\overline{OS}$  output. The the termine its SMBus slave address. The LM95235 does not latch the state of the A0 pin when it is functioning as an input.

### **DIGITAL FILTER**

In order to suppress erroneous remote temperature readings due to noise, the LM95235 incorporates a digital filter for the Remote Temperature Channel. The filter is accessed in the Configuration Register 2, bits D2 (FE1) and D1(FE0). The filter can be set according to the following table.

| FE1 | FE0 | Filter Setting |

|-----|-----|----------------|

| 0   | 0   | Filter Off     |

| 0   | 1   | Reserved       |

| 1   | 0   | Reserved       |

| 1   | 1   | Filter On      |

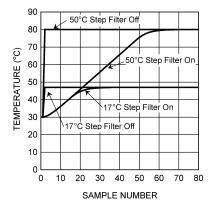

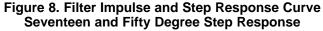

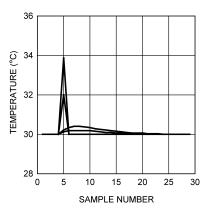

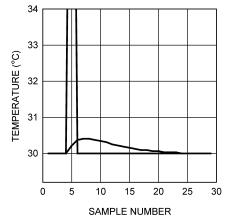

Figure 8 through Figure 10 depict the filter output in response to a step input and an impulse input.

Figure 9. Filter Impulse and Step Response Curve Impulse Response with Input Transients Less Than 4°C

Figure 10. Filter Impulse and Step Response Curve Impulse Response with Input Transients Greater Than 4°C

Figure 11 shows the filter in use in a typical Intel processor on a 65/90 nm process system. Note that the two curves have been purposely offset for clarity. Inserting the filter does not induce an offset as shown.

A. The filter curves were purposely offset for clarity.

### **TEMPERATURE DATA FORMAT**

Temperature data can only be read from the Local and Remote Temperature registers.

Remote temperature data with the digital filter off is represented by an 10-bit plus sign, two's complement word and 11-bit unsigned binary word with an LSb (Least Significant Bit) equal to 0.125°C. The data format is a left justified 16-bit word available in two 8-bit registers. Unused bits report "0".

Remote temperature data with the digital filter on is represented by a 12-bit plus sign, two's complement word and 13-bit unsigned binary word with an LSb (Least Significant Bit) equal to 0.03125°C (1/32°C). The data format is a left justified 16-bit word available in two 8-bit registers. Unused bits report "0".

|             | Digital Output      | •     |

|-------------|---------------------|-------|

| Temperature |                     | 1     |

| •           | Binary              | Hex   |

| +125°C      | 0111 1101 0000 0000 | 7D00h |

| +25°C       | 0001 1001 0000 0000 | 1900h |

| +1°C        | 0000 0001 0000 0000 | 0100h |

| +0.125°C    | 0000 0000 0010 0000 | 0020h |

| 0°C         | 0000 0000 0000 0000 | 0000h |

| -0.125°C    | 1111 1111 1110 0000 | FFE0h |

| Table 4. | 11-Bit. 2' | s Complement                            | (10-Bit Plus | Sian) |

|----------|------------|-----------------------------------------|--------------|-------|

|          |            | • • • • • • • • • • • • • • • • • • • • |              | /     |

Figure 11. Digital Filter Response in a Typical Intel Processor on a 65 nm or 90 nm Process

### Table 4. 11-Bit, 2's Complement (10-Bit Plus Sign) (continued)

| Tomporatura | Digital Output      |       |  |  |  |

|-------------|---------------------|-------|--|--|--|

| Temperature | Binary              | Hex   |  |  |  |

| -1°C        | 1111 1111 0000 0000 | FF00h |  |  |  |

| -25°C       | 1110 0111 0000 0000 | E700h |  |  |  |

| -55°C       | 1100 1001 0000 0000 | C900h |  |  |  |

### Table 5. 11-Bit, Unsigned Binary

| Tomporatura | Digital Output      |       |  |  |  |

|-------------|---------------------|-------|--|--|--|

| Temperature | Binary              | Hex   |  |  |  |

| +255.875°C  | 1111 1111 1110 0000 | FFE0h |  |  |  |

| +255°C      | 1111 1111 0000 0000 | FF00h |  |  |  |

| +201°C      | 1100 1001 0000 0000 | C900h |  |  |  |

| +125°C      | 0111 1101 0000 0000 | 7D00h |  |  |  |

| +25°C       | 0001 1001 0000 0000 | 1900h |  |  |  |

| +1°C        | 0000 0001 0000 0000 | 0100h |  |  |  |

| +0.125°C    | 0000 0000 0010 0000 | 0020h |  |  |  |

| 0°C         | 0000 0000 0000 0000 | 0000h |  |  |  |

### Table 6. 13-Bit, 2's Complement (12-Bit Plus Sign)

| Tomporatura | Digital Output      |       |  |  |  |

|-------------|---------------------|-------|--|--|--|

| Temperature | Binary              | Hex   |  |  |  |

| +125°C      | 0111 1101 0000 0000 | 7D00h |  |  |  |

| +25°C       | 0001 1001 0000 0000 | 1900h |  |  |  |

| +1°C        | 0000 0001 0000 0000 | 0100h |  |  |  |

| +0.03125°C  | 0000 0000 0000 1000 | 0008h |  |  |  |

| 0°C         | 0000 0000 0000 0000 | 0000h |  |  |  |

| -0.03125°C  | 1111 1111 1111 1000 | FFF8h |  |  |  |

| -1°C        | 1111 1111 0000 0000 | FF00h |  |  |  |

| -25°C       | 1110 0111 0000 0000 | E700h |  |  |  |

| -55°C       | 1100 1001 0000 0000 | C900h |  |  |  |

#### Table 7. 13-Bit, Unsigned Binary

| Tomporatura | Digital Output      |       |  |  |  |

|-------------|---------------------|-------|--|--|--|

| Temperature | Binary              | Hex   |  |  |  |

| +255.875°C  | 1111 1111 1110 0000 | FFE0h |  |  |  |

| +255°C      | 1111 1111 0000 0000 | FF00h |  |  |  |

| +201°C      | 1100 1001 0000 0000 | C900h |  |  |  |

| +125°C      | 0111 1101 0000 0000 | 7D00h |  |  |  |

| +25°C       | 0001 1001 0000 0000 | 1900h |  |  |  |

| +1°C        | 0000 0001 0000 0000 | 0100h |  |  |  |

| +0.03125°C  | 0000 0000 0000 1000 | 0008h |  |  |  |

| 0°C         | 0000 0000 0000 0000 | 0000h |  |  |  |

Local Temperature data is represented by a 10-bit plus sign, two's complement word with an LSb (Least Significant Bit) equal to 0.125°C. The data format is a left justified 16-bit word available in two 8-bit registers. Unused bits will always report "0". Local temperature readings greater than +127.875°C are clamped to +127.875°C, they will not roll-over to negative temperature readings.

Copyright © 2006–2013, Texas Instruments Incorporated

| Tamanatana  | Digital Output      | t     |  |  |  |  |  |  |  |

|-------------|---------------------|-------|--|--|--|--|--|--|--|

| Temperature | Binary              | Hex   |  |  |  |  |  |  |  |

| +125°C      | 0111 1101 0000 0000 | 7D00h |  |  |  |  |  |  |  |

| +25°C       | 0001 1001 0000 0000 | 1900h |  |  |  |  |  |  |  |

| +1°C        | 0000 0001 0000 0000 | 0100h |  |  |  |  |  |  |  |

| +0.125°C    | 0000 0000 0010 0000 | 0020h |  |  |  |  |  |  |  |

| 0°C         | 0000 0000 0000 0000 | 0000h |  |  |  |  |  |  |  |

| -0.125°C    | 1111 1111 1110 0000 | FFE0h |  |  |  |  |  |  |  |

| -1°C        | 1111 1111 0000 0000 | FF00h |  |  |  |  |  |  |  |

| -25°C       | 1110 0111 0000 0000 | E700h |  |  |  |  |  |  |  |

| -55°C       | 1100 1001 0000 0000 | C900h |  |  |  |  |  |  |  |

#### Table 8. 11-Bit, 2's Complement (10-Bit Plus Sign)

### SMBDAT OPEN-DRAIN OUTPUT

The SMBDAT output is an open-drain output and does not have internal pull-ups. A "high" level will not be observed on this pin until pull-up current is provided by some external source, typically a pull-up resistor. Choice of resistor value depends on many system factors but, in general, the pull-up resistor should be as large as possible without effecting the SMBus desired data rate. This will minimize any internal temperature reading errors due to internal heating of the LM95235. The maximum resistance of the pull-up to provide a 2.1V high level, based on LM95235 specification for High Level Output Current with the supply voltage at 3.0V, is 82 k $\Omega$  (5%) or 88.7 k $\Omega$  (1%).

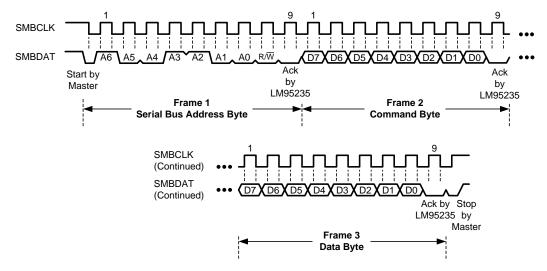

# T\_CRIT OUTPUT AND TCRIT LIMIT

The LM95235's  $\overline{T_CRIT}$  pin is an active-low open-drain output that is triggered when the local and/or the remote temperature conversion is above the limits defined by the Remote and/or Local Limit registers. The state of the  $\overline{T_CRIT}$  pin will return to the HIGH state when both the Local and Remote temperatures are below the values programmed into the Limit Registers less the value in the Common Hysteresis Register. Additionally, if the remote temperature exceeds the value in the Remote TCRIT Limit Register the Status Bit for Remote TCRIT (RTCRIT), in Status Register 1, is set to 1. In the same way if the local temperature exceeds the value in the Local Shared OS and TCRIT Limit Register the Status Bit for the Shared Local OS and TCRIT (LOC) bit in Status Register 1 is set to 1. The T\_CRIT output and the Status Register flags are updated after every Local and Remote temperature conversion. See Figure 12

Figure 12. T\_CRIT Comparator Temperature Response Diagram

NSTRUMENTS

FXAS

### **OS OUTPUT AND OS LIMIT**

The LM95235's  $\overline{OS}/A0$  pin is selected as an  $\overline{OS}$  digital output as described in SMBus INTERFACE. As an  $\overline{OS}$  pin, it is activated whenever the local and/or remote temperature conversion is above the limits defined by the Limit registers. If the remote temperature exceeds the value in the Remote OS Limit Register the Status Bit for Remote OS (ROS) in Status Register 1 is set to 1. In the same way if the local temperature exceeds the value in the Local Shared OS and TCRIT Limit Register the Status Bit for the Shared Local OS and TCRIT (LOC) bit in Status Register 1 is set to 1. The state of the T\_CRIT pin output will return to the HIGH state when both the Local and Remote temperatures are below the values programmed into the Limit Registers less the value in the Common Hysteresis Register. The  $\overline{OS}$  output and the Status Register flags are updated after every Local and Remote temperature conversion. See Figure 13.

Figure 13. OS Temperature Response Diagram

### DIODE FAULT DETECTION

The LM95235 is equipped with operational circuitry designed to detect fault conditions concerning the remote diodes. In the event that the D+ pin is detected as shorted to GND, D-,  $V_{DD}$  or D+ is floating, the Remote Temperature reading is -128.000°C if signed format is selected and +255.875°C if unsigned format is selected. In addition, the Status Register 1 bit D2 is set.

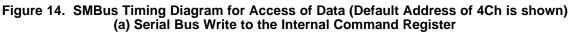

### COMMUNICATING WITH THE LM95235

The data registers in the LM95235 are selected by the Command Register. At power-up the Command Register is set to "00", the location for the Read Local Temperature Register. The Command Register latches the last location it was set to. Each data register in the LM95235 falls into one of four types of user accessibility:

- 1. Read only

- 2. Write only

- 3. Write/Read same address

- 4. Write/Read different address

A Write to the LM95235 will always include the address byte and the command byte. A write to any register requires one data byte.

**Reading** the LM95235 can take place either of two ways:

- 1. If the location latched in the Command Register is correct (most of the time it is expected that the Command Register will point to one of the Read Temperature Registers because that will be the data most frequently read from the LM95235), then the read can simply consist of an address byte, followed by retrieving the data byte.

- 2. If the Command Register needs to be set, then an address byte, command byte, repeat start, and another address byte will accomplish a read.

# LM95235 LM95235-Q1 SNIS142F – APRIL 2006– REVISED MARCH 2013

www.ti.com

The data byte has the most significant bit first. At the end of a read, the LM95235 can accept either acknowledge or No Acknowledge from the Master (No Acknowledge is typically used as a signal for the slave that the Master has read its last byte). When retrieving all 11 bits from a previous remote diode temperature measurement, the master must insure that all 11 bits are from the same temperature conversion. This may be achieved by reading the MSB register first. The LSB will be locked after the MSB is read. The LSB will be unlocked after being read. If the user reads MSBs consecutively, each time the MSB is read, the LSB associated with that temperature will be locked in and override the previous LSB value locked-in.

Figure 15. SMBus Timing Diagram for Access of Data (Default Address of 4Ch is shown) (b) Serial Bus Write to the Internal Command Register Followed by a Data Byte

Figure 16. SMBus Timing Diagram for Access of Data (Default Address of 4Ch is shown) (c) Serial Bus Byte Read from a Register with the Internal Command Register Preset to Desired Value

Figure 17. SMBus Timing Diagram for Access of Data (Default Address of 4Ch is shown) (d) Serial Bus Write Followed by a Repeat Start and Immediate Read

### SERIAL INTERFACE RESET

In the event that the SMBus Master is RESET while the LM95235 is transmitting on the SMBDAT line, the LM95235 must be returned to a known state in the communication protocol. This may be done in one of two ways:

- When SMBDAT is LOW, the LM95235 SMBus state machine resets to the SMBus idle state if either SMBDAT or SMBCLK are held low for more than 35 ms (t<sub>TIMEOUT</sub>). Note that according to SMBus specification 2.0 all devices are to timeout when either the SMBCLK or SMBDAT lines are held low for 25 -35 ms. Therefore, to insure a timeout of all devices on the bus the SMBCLK or SMBDAT lines must be held low for at least 35 ms.

- When SMBDAT is HIGH, have the master initiate an SMBus start. The LM95235 will respond properly to an SMBus start condition at any point during the communication. After the start the LM95235 will expect an SMBus Address address byte.

### **ONE-SHOT CONVERSION**

The One-Shot register is used to initiate a single conversion and comparison cycle when the device is in standby mode, after which the device returns to standby. This is not a data register and it is the write operation that causes the one-shot conversion. The data written to this address is irrelevant and is not stored. A zero will always be read from this register.

### LM95235 REGISTERS

Command register selects which registers will be read from or written to. Data for this register should be transmitted during the Command Byte of the SMBus write communication. POR means Power-On Reset.

#### P0-P7: Command

| P7      | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|---------|----|----|----|----|----|----|----|

| Command |    |    |    |    |    |    |    |

### Table 9. Register Summary

|                                  | 1                        |                           |                   |                         | -              |                                                                                  |

|----------------------------------|--------------------------|---------------------------|-------------------|-------------------------|----------------|----------------------------------------------------------------------------------|

| Register Name                    | Read<br>Address<br>(Hex) | Write<br>Address<br>(Hex) | No.<br>of<br>bits | POR<br>Default<br>(Hex) | Read/<br>Write | Description                                                                      |

| TEMPERATURE SIGNED VALUE         | REGISTER                 | S                         |                   |                         |                |                                                                                  |

| Local Temp MSB                   | 0x00                     | NA                        | 8                 | -                       | RO             | Supports SMBus byte                                                              |

| Local Temp LSB                   | 0x30                     | NA                        | 3                 | -                       | RO             | All unused bits are reported as "0".                                             |

| Remote Temp MSB – Signed         | 0x01                     | NA                        | 8                 | -                       | RO             | Supports SMBus byte                                                              |

| Remote Temp LSB – Signed         | 0x10                     | NA                        | 5/3               | -                       | RO             | All unused bits are reported as "0".                                             |

| TEMPERATURE UNSIGNED VAL         | UE REGIST                | ERS                       |                   |                         |                |                                                                                  |

| Remote Temp MSB – Unsigned       | 0x31                     | NA                        | 8                 | -                       | RO             | Supports SMBus byte reads                                                        |

| Remote Temp LSB – Unsigned       | 0x32                     | NA                        | 5/3               | -                       | RO             | All unused bits are reported as "0".                                             |

| DIODE CONFIGURATION REGIS        | TERS                     | • • • •                   |                   | •                       |                |                                                                                  |

| Configuration Register 2         | 0xBF                     | 0xBF                      | 5                 | 0x1F                    | R/W            | Filter Enable, Diode Model Select, Diode Fault Mask; Pin 6 OS/A0 function select |

| Remote Offset High Byte          | 0x11                     | 0x11                      | 8                 | 0x00                    | R/W            | 2's Complement                                                                   |

| Remote Offset Low Byte           | 0x12                     | 0x12                      | 3                 | 0x00                    | R/W            | 2's Complement<br>All unused bits are reported as "0".                           |

| GENERAL CONFIGURATION RE         | GISTERS                  |                           |                   |                         |                |                                                                                  |

| Configuration Register 1         | 0x03/<br>0x09            | 0x09/<br>0x03             | 5                 | 0x00                    | R/W            | STOP/RUN , Remote TCRIT mask, Remote OS mask, Local TCRIT mask, Local OS mask    |

| Conversion Rate                  | 0x04/0x0<br>A            | 0x04/0x0<br>A             | 2                 | 0x02                    | R/W            | Continuous or specific settings                                                  |

| One-Shot                         | NA                       | 0x0F                      | -                 | -                       | WO             | A write to this register activates one conversion if STOP/RUN bit = 1.           |

| STATUS REGISTERS                 |                          |                           |                   |                         |                |                                                                                  |

| Status Register 1                | 0x02                     | NA                        | 5                 | -                       | RO             | Busy bit, and status bits                                                        |

| Status Register 2                | 0x33                     | NA                        | 2                 | -                       | RO             | Not Ready bit, Diode detect bit                                                  |

| LIMIT REGISTERS                  |                          |                           |                   |                         |                |                                                                                  |

| Remote OS Limit                  | 0x07/<br>0x0D            | 0x0D/<br>0x07             | 8                 | 0x55                    | R/W            | Unsigned 0 to 255°C<br>Default 85°C                                              |

| Local Shared OS and T_Crit Limit | 0x20                     | 0x20                      | 7                 | 0x55                    | R/W            | Unsigned 0 to 127°C<br>Default 85°C                                              |

| Remote T_Crit Limit              | 0x19                     | 0x19                      | 8                 | 0x6E                    | R/W            | Unsigned 0 to 255°C<br>Default 110°C                                             |

| Common Hysteresis                | 0x21                     | 0x21                      | 5                 | 0x0A                    | R/W            | up to 31°C                                                                       |

| IDENTIFICATION REGISTERS         |                          |                           |                   | ,                       |                | · · · · · · · · · · · · · · · · · · ·                                            |

| Manufacturer ID                  | 0xFE                     |                           |                   | 0x01                    | RO             | Always returns 0x01                                                              |

|                                  |                          |                           |                   | 0xB1                    | RO             | Returns revision number.                                                         |

# LOCAL and REMOTE MSB and LSB TEMPERATURE REGISTERS

#### Table 10. Local Temperature MSB

(Read Only Address 00h)

| 10-bit plus sign forn | nat: |    |    |    |    |    |    |    |

|-----------------------|------|----|----|----|----|----|----|----|

| BIT                   | D7   | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| Value                 | SIGN | 64 | 32 | 16 | 8  | 4  | 2  | 1  |

Temperature Data: LSb = 1°C.

#### Table 11. Local Temperature LSB

(Read Only Address 30h)

| 10-bit plus sign form | nat: |      |       |    |    |    |    |    |

|-----------------------|------|------|-------|----|----|----|----|----|

| BIT                   | D7   | D6   | D5    | D4 | D3 | D2 | D1 | D0 |

| Value                 | 0.5  | 0.25 | 0.125 | 0  | 0  | 0  | 0  | 0  |

Temperature Data: LSb = 0.125°C.

#### Table 12. Signed Remote Temperature MSB

(Read Only Address 01h)

| 12-bit plus sign form | nat: |    |    |    |    |    |    |    |

|-----------------------|------|----|----|----|----|----|----|----|

| BIT                   | D7   | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| Value                 | SIGN | 64 | 32 | 16 | 8  | 4  | 2  | 1  |

Temperature Data: LSb = 1°C.

#### Table 13. Signed Remote Temperature LSB, Filter On

(Read Only Address 10h)

12-bit plus sign binary formats with filter on:

| BIT   | D7  | D6   | D5    | D4     | D3      | D2 | D1 | D0 |

|-------|-----|------|-------|--------|---------|----|----|----|

| Value | 0.5 | 0.25 | 0.125 | 0.0625 | 0.03125 | 0  | 0  | 0  |

#### Table 14. Signed Remote Temperature LSB, Filter Off

(Read Only Address 10h)

12-bit plus sign binary formats with filter off:

| BIT   | D7  | D6   | D5    | D4 | D3 | D2 | D1 | D0 |

|-------|-----|------|-------|----|----|----|----|----|

| Value | 0.5 | 0.25 | 0.125 | 0  | 0  | 0  | 0  | 0  |

Temperature Data: LSb = 0.125°C filter off or 0.03125°C filter on.

... ....

#### Table 15. Unsigned Remote Temperature MSB

(Read Only Address 31h)

| 13-bit unsigned forr | nat: |    |    |    |    |    |    |    |

|----------------------|------|----|----|----|----|----|----|----|

| BIT                  | D7   | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| Value                | 128  | 64 | 32 | 16 | 8  | 4  | 2  | 1  |

Temperature Data: LSb = 1°C.

#### Table 16. Unsigned Remote Temperature LSB, Filter On

(Read Only Address 32h)

| 13-bit unsigned bina | ary formats with | filter on: |    |    |  |

|----------------------|------------------|------------|----|----|--|

| BIT                  | D7               | D6         | D5 | D4 |  |

| BIT   | D7  | D6   | D5    | D4     | D3      | D2 | D1 | D0 |

|-------|-----|------|-------|--------|---------|----|----|----|

| Value | 0.5 | 0.25 | 0.125 | 0.0625 | 0.03125 | 0  | 0  | 0  |

TEXAS INSTRUMENTS

www.ti.com

#### Table 17. Unsigned Remote Temperature LSB, Filter Off

| (Read Only Address 32h) |  |

|-------------------------|--|

| 10111 1 111 1           |  |

| 13-bit unsigned bina | ary formats with | filter off: |       |    |    |    |    |    |

|----------------------|------------------|-------------|-------|----|----|----|----|----|

| BIT                  | D7               | D6          | D5    | D4 | D3 | D2 | D1 | D0 |

| Value                | 0.5              | 0.25        | 0.125 | 0  | 0  | 0  | 0  | 0  |

Temperature Data: LSb = 0.125°C filter off or 0.03125°C filter on.

For data synchronization purposes, the MSB register should be read first if the user wants to read both MSB and LSB registers. The LSB will be locked after the MSB is read. The LSB will be unlocked after being read. If the user reads MSBs consecutively, each time the MSB is read, the LSB associated with that temperature will be locked in and override the previous LSB value locked-in.

# **DIODE CONFIGURATION REGISTERS**

#### Table 18. Configuration Register 2

(Read/write Address BFh)

| D7 | D6                    | D5            | D4          | D3              | D2   | D1   | D0 |

|----|-----------------------|---------------|-------------|-----------------|------|------|----|

| 0  | OS/A0 Function Select | OS Fault Mask | T_CRIT Mask | TruTherm Select | RFE1 | RFE0 | 1  |

| Bits | Name                                 | Description                                                                                                                                                                                     |

|------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | Reserved                             | Reports "0" when read.                                                                                                                                                                          |

| 6    | OS/A0 Function Select                | 0: Address (A0) function is enabled<br>1: Over-temperature Shutdown (OS) is enabled                                                                                                             |

| 5    | Diode Fault Mask for OS              | 0: Off<br>1: On                                                                                                                                                                                 |

| 4    | Diode Fault Mask for T_CRIT          | 0: Off<br>1: On                                                                                                                                                                                 |

| 3    | Remote Diode TruTherm<br>Mode Select | 0: Selects Diode Model 2, MMBT3904, with TruTherm technology disabled.<br>1: Selects Diode Model 1, A typical Intel Processor, with 65 nm or 90 nm technology, and TruTherm technology enabled. |

| 2-1  | Remote Filter Enable                 | 00: Filter Disable<br>01: Reserved<br>10: Reserved<br>11: Filter Enable                                                                                                                         |

| 0    | Reserved                             | Reports "1" when read.                                                                                                                                                                          |

Power up default is 1Fh.

### Table 19. Remote Offset High Byte (2's Complement)

(R/W Address 11h)

| TO-bit plus sign for | nal. |    |    |    |    |    |    |    |

|----------------------|------|----|----|----|----|----|----|----|

| BIT                  | D7   | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| Value                | SIGN | 64 | 32 | 16 | 8  | 4  | 2  | 1  |

Power up default is 00h.

#### Table 20. Remote Offset Low Byte (2's Complement)

10-bit plus sign format:(R/W Address 12h)

| BIT   | D7   | D6   | D5    | D4 | D3 | D2 | D1 | D0 |

|-------|------|------|-------|----|----|----|----|----|

| Value | 0.50 | 0.25 | 0.125 | 0  | 0  | 0  | 0  | 0  |

Power up default is 00h. LSb = 0.125°C.

# **GENERAL CONFIGURATION REGISTERS**

# Table 21. Configuration Register 1

(Read/write Address 03h/09h or 09h/03h):

| D7 | D6                  | D5     | D4                 | D        | 3               | D2                                   | D1            | D0 |  |  |  |

|----|---------------------|--------|--------------------|----------|-----------------|--------------------------------------|---------------|----|--|--|--|

| 0  | STOP/RUN            | 0      | Remote T_CRIT Mask | Remote 0 | OS Mask         | Local T_CRIT Mask                    | Local OS Mask | 0  |  |  |  |

|    | Bits Name           |        |                    |          |                 | Description                          |               |    |  |  |  |

|    | 7                   | Reserv | red                |          | Reports "0"     | when read.                           |               |    |  |  |  |

|    | 6 STOP/RUN          |        |                    |          |                 | 0: Active / Converting<br>1: Standby |               |    |  |  |  |

|    | 5                   | Reserv | red                |          | Reports "0"     | when read.                           |               |    |  |  |  |

|    | 4                   | Remot  | e T_CRIT Mask      |          | 0: Off<br>1: On |                                      |               |    |  |  |  |

|    | 3                   | Remot  | e OS Mask          |          | 0: Off<br>1: On |                                      |               |    |  |  |  |

|    | 2 Local T_CRIT Mask |        |                    |          | 0: Off<br>1: On |                                      |               |    |  |  |  |

|    | 1 Local OS Mask     |        |                    |          | 0: Off<br>1: On |                                      |               |    |  |  |  |

|    | 0                   | Reserv | red                |          | Reports "0"     | when read.                           |               |    |  |  |  |

Power up default is 00h.

### Table 22. Conversion Rate Register

(Read/write Address 04h/0Ah or 0Ah/04h):

2-bit format:

| BIT   | D7 | D6 | D5 | D4 | D3 | D2 | D1  | D0  |

|-------|----|----|----|----|----|----|-----|-----|

| Value | 0  | 0  | 0  | 0  | 0  | 0  | MSb | LSb |

| Bits | Name            | Description                                                                                                                                                                                                     |

|------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2  | Reserved        | Reports "0" when read.                                                                                                                                                                                          |

| 1:0  | Conversion Rate | <ul> <li>00: Continuous (33 ms typical when remote diode is missing or fault or 63 ms typical with remote diode connected)</li> <li>01: 0.364 seconds</li> <li>10: 1 second</li> <li>11: 2.5 seconds</li> </ul> |

Power up default is 02h (1 second).

# Table 23. One Shot Register

(Write Only Address 0Fh):

Writing to this register will start one conversion if the device is in standby mode (i.e. STOP/RUN bit = 1).

TEXAS INSTRUMENTS

www.ti.com

# STATUS REGISTERS

### Table 24. Status Register 1

(Read Only Address 02h):